Logic Level Shifting Basics

Mixing high and low logic level voltages in communication and GPIO

Overview

The latest digital device designs keep getting smaller, faster, and more efficient. Mainstay 5 V logic is joined by ever lower voltage standards like 3.3 V, 2.5 V, 1.8 V, and lower, resulting in the need for a methodology that allows mismatched systems to reliably and efficiently communicate. Designers need to ensure that a logical 1 or logical 0 is achievable in a predictable manner across these platforms.

Translation/isolation between binary or two-stage logic voltages promotes predictable circuit behavior. Designers may reason that a 3.3 V signal on a 5 V pin “should work” but that is not always the case under all conditions. Conversely, 5 V on a 3.3 V, 5 V tolerant pin certainly works in most instances, but this method is more expensive due to additional components and “burning off” the excess voltage in some cases.

Is There an Alternative?

Active Translator/Level Shifting devices solve common translation issues and may even provide additional useful functions such as inversion, push-pull output, tri-state, or differential functionality. But how about something less complex that allows for wider logic voltage levels and bidirectional communication? A discrete, compact MOSFET can accomplish translation at high frequency and efficiency. Level shifting for communication such as I²C and direct GPIO pin to pin connection is achieved using these inexpensive semiconductors and a few additional passive devices. Properly chosen MOSFETs allow for higher logic voltages, such as 12 V or 18 V, that may also be used for monitoring automotive circuits as an example.

Note: I²C in Hs-Mode (High speed) may require more refined components such as NXP’s PCA9306 bidirectional translator.

Example: BS170 (N-Channel Enhancement Mode Field Effect Transistor)

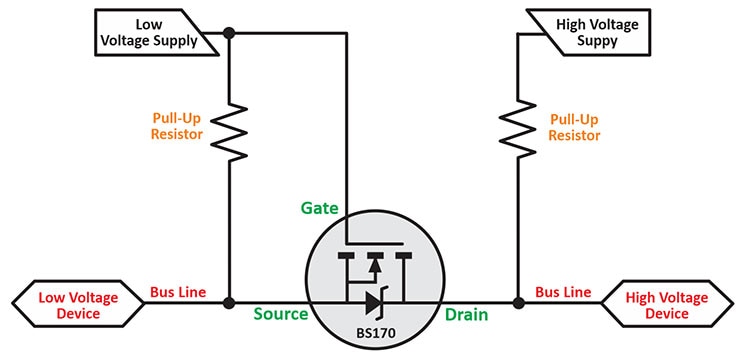

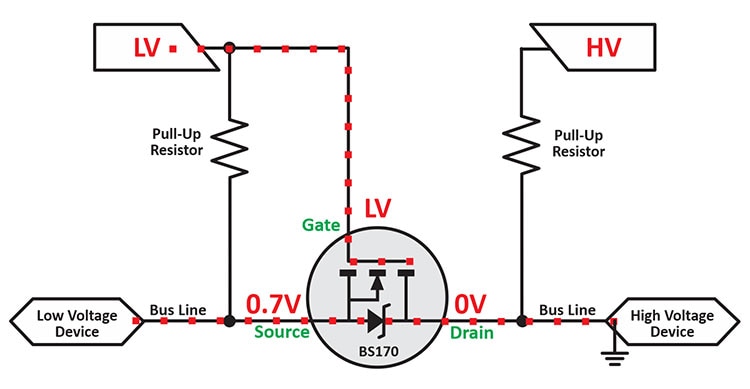

The BS170 is designed to minimize on-state resistance while providing reliable and fast switching performance suited for low-voltage, low current switching applications. Figure 1 shows the connections needed to perform basic communication or GPIO logic level shifting.

Figure 1: Basic, single bus, level translation MOSFET circuit.

Figure 1: Basic, single bus, level translation MOSFET circuit.

The logic high levels on each side of the MOSFET are achieved by pull-up resistors to their respective supplies providing conversion of fast mode (400 kHz) I²C signals or other similarly fast digital interfaces. The gate of the MOSFET is held at the low voltage supply level. When no device is pulling down the bus line, the bus line at the MOSFET’s source is pulled up by the low voltage pull-up resistors. The MOSFET’s Gate/Source voltage (VGS) is below the threshold, and the MOSFET is not conducting. This allows the bus line at the MOSFET’s drain to be pulled up by the higher-voltage pull-up resistor. The bus lines on each side of the MOSFET are held HIGH but at different voltage levels. See Figure 2.

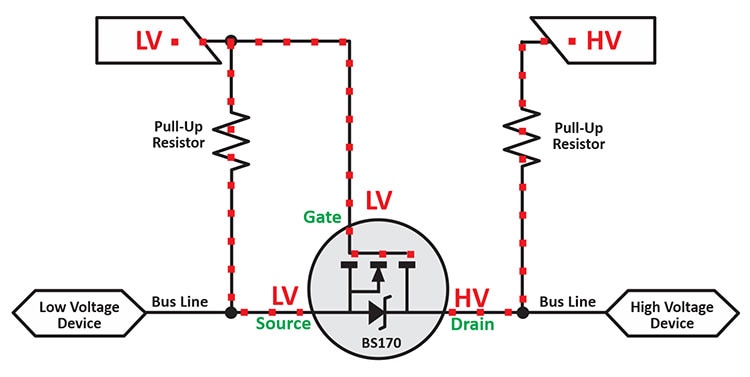

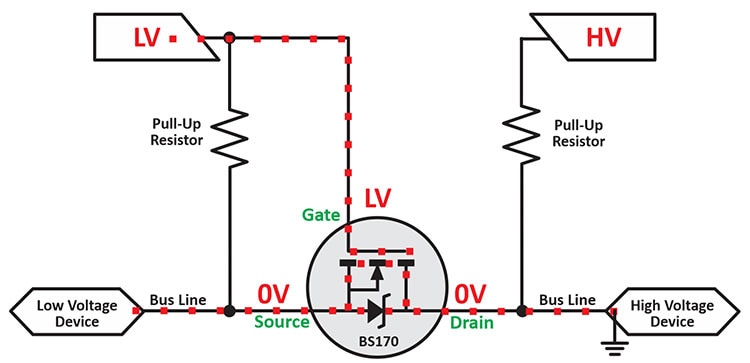

Figure 2: Logical HIGH voltage translation.

Figure 2: Logical HIGH voltage translation.

If the low voltage device pulls down the bus line at the MOSFET’s source and the gate remains at the low voltage supply, VGS rises above the threshold and the MOSFET starts to conduct. The bus line at the MOSFET’s drain is now pulled down as well. Refer to Figure 3.

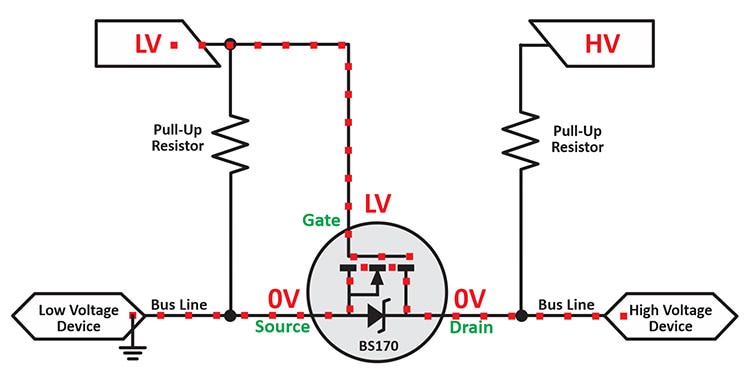

Figure 3: Logical LOW voltage translation initiated by low voltage device.

Figure 3: Logical LOW voltage translation initiated by low voltage device.

If the high voltage device pulls down the bus line at the MOSFET’s drain, the MOSFET’s substrate diode allows the source to also be partially pulled down due to a small amount of voltage dropped across the diode. See Figure 4.

Figure 4: Near logical LOW voltage translation initiated by a high voltage device.

Figure 4: Near logical LOW voltage translation initiated by a high voltage device.

When the MOSFET’s source is partially pulled down, the VGS rises above the threshold and the MOSFET starts to conduct effectively bypassing the substrate diode. See Figures 5.

Figure 5: Full logical LOW voltage translation initiated by high voltage device.

Figure 5: Full logical LOW voltage translation initiated by high voltage device.

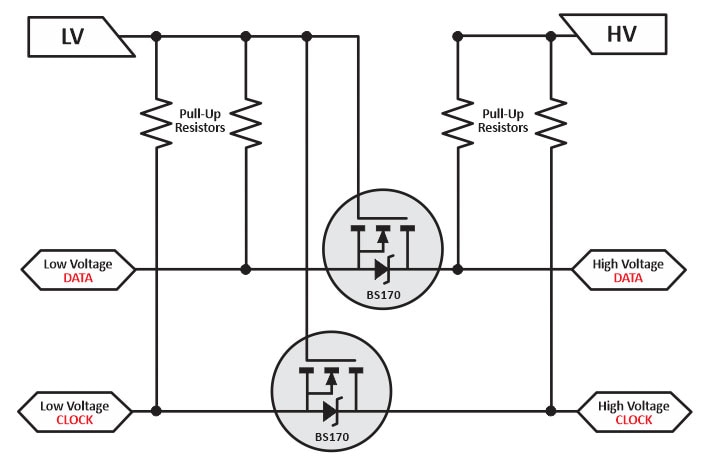

The three states show transferred logic levels in both directions of the bus system, independent of the driving section. Many combinations of high and low voltage supplies are possible depending upon the capabilities of the MOSFET. Whether the logic level conflict involves point-to-point GPIO, sensor output, or bidirectional multi-line communication, MOSFET level shifters are useful tools. Figure 5 demonstrates the implementation of a translated, two-line, bidirectional communication circuit using two MOSFETs.

Figure 6: Two-line bidirectional translated data communication circuit.

Figure 6: Two-line bidirectional translated data communication circuit.

Isolation

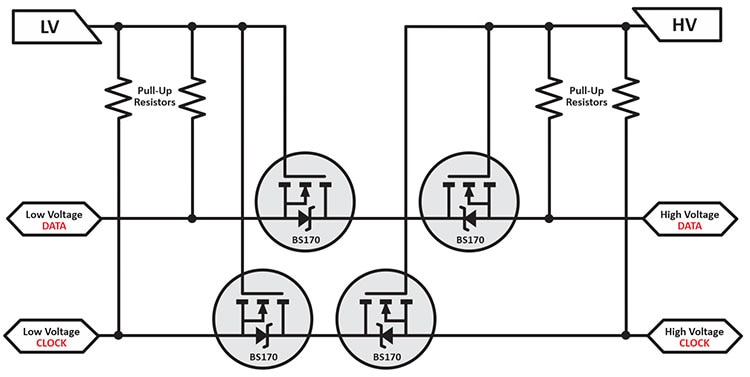

To prevent random logic levels in the event the high voltage device is powered down, or a power loss occurs in the high voltage supply, additional MOSFETs may be implemented “drain to drain” to isolate the high voltage logic bus lines.

Figure 7: Isolated bus lines in a translated data communication circuit.

Figure 7: Isolated bus lines in a translated data communication circuit.

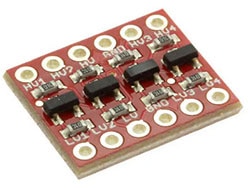

Development boards

To learn more about logic level translation, several manufacturers produce development boards populated with MOSFETs or logic translation devices along with the needed peripheral passive devices to allow for quick connection and experimentation.

Summary

A properly chosen MOSFET and pull-up resistor is key to the success of this simple but effective method of logic translation. Typical device datasheets contain the information needed for experimentation. Pull-up resistors for the BS170 in the range of 4.7 Kohm to 10 Kohm may work well in most cases. Dedicated logic level converter ICs may also provide extra features such as 15 kV ESD protection on I/O and supply voltage inputs.

Have questions or comments? Continue the conversation on TechForum, DigiKey's online community and technical resource.

Visit TechForum