Le LPC80x de NXP Semiconductors appartient à une famille de microcontrôleurs 32 bits basés sur un cœur Arm Cortex-M0+ économique, fonctionnant à des fréquences de processeur jusqu'à 15 MHz. La famille LPC80x fait partie de la plateforme edge computing EdgeVerse™ de NXP. La famille de microcontrôleurs LPC80x prend en charge jusqu'à 32 Ko de mémoire Flash et jusqu'à 4 Ko de mémoire SRAM.

Le LPC80x de NXP Semiconductors appartient à une famille de microcontrôleurs 32 bits basés sur un cœur Arm Cortex-M0+ économique, fonctionnant à des fréquences de processeur jusqu'à 15 MHz. La famille LPC80x fait partie de la plateforme edge computing EdgeVerse™ de NXP. La famille de microcontrôleurs LPC80x prend en charge jusqu'à 32 Ko de mémoire Flash et jusqu'à 4 Ko de mémoire SRAM.

Cette gamme se caractérise par un cœur optimisé en termes de puissance, une empreinte compacte dans les boîtiers les plus répandus et des options de décalage de niveau grâce à ses rails d'alimentation distincts. Parmi les compléments périphériques du LPC80x, on trouve un moteur CRC, des interfaces de bus I2C, jusqu'à deux USART, une interface SPI, une interface tactile capacitive, un temporisateur multi-débit, un temporisateur à auto activation, un compteur/temporisateur 32 bits à usage général, un CAN 12 bits, un CNA 10 bits, un comparateur analogique, des ports d'E/S à fonctions configurables grâce à une matrice de commutation, un moteur de correspondance de motifs d'entrée, une unité logique programmable (PLU) et jusqu'à 30 broches d'E/S à usage général.

| Fonctionnalités |

- Système

- Processeur Arm Cortex-M0+ (révision r0p1), fonctionnant à des fréquences jusqu'à 15 MHz avec multiplicateur monocycle et port d'E/S monocycle rapide ; contrôleur d'interruption vectorisé imbriqué (NVIC) intégré

- Temporisateur système

- Matrice multicouche AHB

- Interface SWD (Serial Wire Debug) avec quatre points d'interruption et deux points de contrôle ; prise en charge de JTAG BSDL (Boundary Scan Description Langage)

- Périphériques numériques

- Interface GPIO haute vitesse connectée au bus d'E/S du processeur Arm Cortex-M0+ avec jusqu'à 30 broches GPIO et des résistances d'excursion basse/haute configurables, un mode à drain ouvert programmable et un onduleur d'entrée ; le contrôle de direction GPIO prend en charge la définition, l'effacement et le basculement de bits individuels

- Circuit d'attaque de sortie à source de courant élevé (20 mA) sur les trois broches

- Capacité de génération d'interruption GPIO avec fonctionnalité de mise en correspondance booléenne sur huit entrées GPIO (LPC804)

- Matrice de commutation pour configuration flexible de chaque fonction de broches E/S

- Moteur CRC

- Interface tactile capacitive (LPC804)

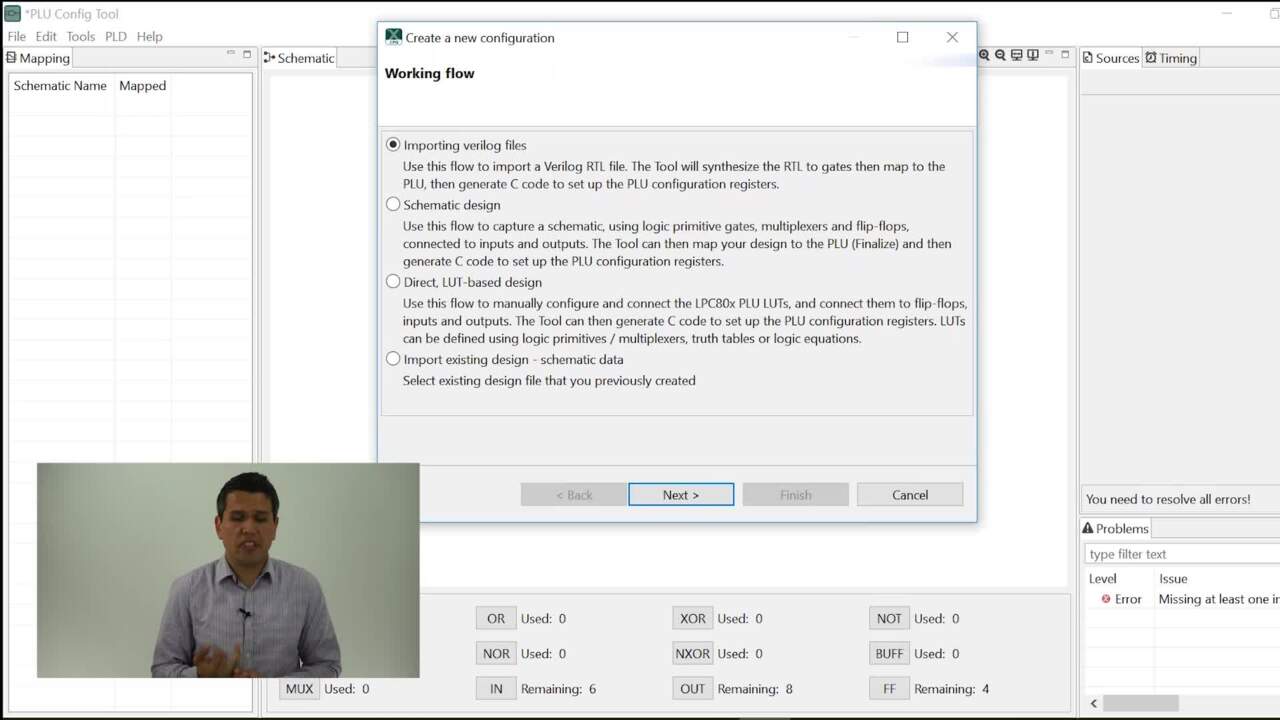

- Unité PLU pour créer de petits réseaux logiques combinatoires ou séquentiels, y compris des machines à état simple (LPC804)

|

|

- Prise en charge de l'API pour mémoire ROM

- Chargeur d'amorçage

- Prise en charge de la programmation Flash en application (IAP)

- Prise en charge de la programmation in-situ (ISP) via un USART

- API de mémoire ROM intégrée pour division entière

- API d'oscillateur non piloté (FRO)

- Mémoire

- Mémoire de programmation Flash intégrée de 32 Ko max.

- Protection en lecture du code (CRP)

- Jusqu'à 4 Ko de mémoire SRAM

- Double alimentation E/S (LPC802M011JDH20, LPC804M111JDH24) :

- Alimentations indépendantes de chaque côté du boîtier permettant le décalage du niveau des signaux d'un domaine de la tension extérieur à un autre ou un interfaçage direct avec des périphériques hors puce fonctionnant à différents niveaux d'alimentation

|

| Applications |

- Passerelles de capteur

- Industrie

- Contrôleurs de jeu

- Applications 8/16 bits

- Grand public

|

|

- Commandes de climatisation

- Commandes de moteur

- Ordinateurs portables et dispositifs corporels

- Éclairage

- Applications de sécurité et de protection contre le feu

|

![]() Le LPC80x de NXP Semiconductors appartient à une famille de microcontrôleurs 32 bits basés sur un cœur Arm Cortex-M0+ économique, fonctionnant à des fréquences de processeur jusqu'à 15 MHz. La famille LPC80x fait partie de la plateforme edge computing EdgeVerse™ de NXP. La famille de microcontrôleurs LPC80x prend en charge jusqu'à 32 Ko de mémoire Flash et jusqu'à 4 Ko de mémoire SRAM.

Le LPC80x de NXP Semiconductors appartient à une famille de microcontrôleurs 32 bits basés sur un cœur Arm Cortex-M0+ économique, fonctionnant à des fréquences de processeur jusqu'à 15 MHz. La famille LPC80x fait partie de la plateforme edge computing EdgeVerse™ de NXP. La famille de microcontrôleurs LPC80x prend en charge jusqu'à 32 Ko de mémoire Flash et jusqu'à 4 Ko de mémoire SRAM.