Implémenter l'edge computing basse consommation et hautes performances avec les FPGA à technologie Quantum d'Efinix

Avec la contribution de Rédacteurs nord-américains de DigiKey

2020-03-17

Le cloud computing classique présente des problèmes de latence, de sécurité des données, de confidentialité de l'utilisateur final, de bande passante disponible et de fiabilité de la connectivité. Pour les résoudre, les concepteurs et les architectes système s'orientent vers l'edge computing. Cependant, l'edge computing présente aussi son lot de défis : coût, taille, performances et consommation énergétique, mais aussi évolutivité, flexibilité et possibilité de mise à niveau. Cela est particulièrement vrai lorsque les concepteurs souhaitent effectuer davantage de traitement d'images et implémenter plus d'algorithmes d'intelligence artificielle (IA) et d'apprentissage automatique (ML), et ce, plus près de la source de données.

En conséquence, les concepteurs voient au-delà des microcontrôleurs (MCU) ou des processeurs d'application (AP) traditionnels, et s'intéressent aux réseaux de portes programmables par l'utilisateur (FPGA) avec leurs capacités de traitement parallèle. Les améliorations constantes dans la conception et la mise en œuvre des FPGA impliquent qu'ils peuvent désormais satisfaire à un grand nombre voire à la totalité de ces exigences, soit en tant que dispositifs autonomes, soit conjointement avec des microcontrôleurs et des processeurs d'application. Cela étant dit, nombreux sont les concepteurs qui ne connaissent pas bien les FPGA et s'inquiètent de la courbe d'apprentissage qu'ils impliquent.

Cet article aborde brièvement la migration du cloud vers l'edge computing, et les raisons pour lesquelles les architectures de traitement traditionnelles sont à la traîne en ce qui concerne le traitement d'images, l'intelligence artificielle et l'apprentissage automatique. Il offre ensuite un aperçu des FPGA et des raisons pour lesquelles ils présentent un avantage architectural pour ces applications en périphérie à grand volume de données. Enfin, il présente une nouvelle approche des FPGA — la technologie Quantum d'Efinix — et explique comment l'appliquer.

Pourquoi l'edge computing ?

Dans le cloud computing traditionnel, les données sont regroupées depuis une myriade d'emplacements distants et acheminées vers un système basé sur le cloud, à des fins de stockage et d'analyse. Cependant, cette approche présente de nombreux inconvénients, notamment les coûts de transmission de grandes quantités de données brutes, le maintien de l'intégrité et de la sécurité de ces données lors de leur acheminement, les latences de réponse, les préoccupations relatives à la confidentialité des utilisateurs, des connexions à Internet qui manquent souvent de fiabilité et une utilisation sous-optimale de la bande passante disponible.

Comme son nom le suggère, l'edge computing signifie déplacer le traitement — le calcul et l'analyse — au plus près de la périphérie d'Internet, précisément à l'endroit où les données sont générées, analysées, regroupées et appliquées. Le terme « edge computing » n'est pas spécifique à une application ou à un dispositif. Les concepteurs peuvent choisir un traitement en périphérie exclusivement, ou un équilibre entre le cloud et la périphérie, selon ce qui convient.

Les applications en périphérie incluent les usines intelligentes, les villes intelligentes, les maisons intelligentes et les transports intelligents, pour n'en mentionner que quelques-unes. Les dispositifs en périphérie s'étendent des grands serveurs périphériques haut de gamme aux systèmes de capteurs et d'actionneurs relativement compacts, situés à l'extrême périphérie d'Internet, là où les données sont générées.

L'avantage des FPGA

En matière de calcul, les processeurs traditionnels sont extrêmement efficaces en ce qui concerne la prise de décision et les tâches séquentielles, mais ils sont terriblement inefficaces pour ce qui est de nombreux algorithmes de traitement de données, comme ceux utilisés pour le traitement d'images, l'IA et le ML. Ces tâches peuvent souvent être divisées en pipelines de traitement massivement parallèles (par opposition aux tâches séquentielles). En l'occurrence, ce sont précisément ces applications qui migrent vers la périphérie et l'extrême périphérie.

Le fait que les FPGA puissent être programmés (configurés) pour implémenter n'importe quelle combinaison de fonctions leur permet d'exécuter des algorithmes de traitement d'images, d'IA et de ML d'une façon massivement parallèle, ce qui minimise la latence tout en réduisant la consommation énergétique. Outre leur structure programmable principale, les FPGA sont équipés de blocs de traitement des signaux numériques (DSP) intégrés contenant des multiplicateurs spéciaux qui accélèrent considérablement les applications DSP intensives. Les FPGA intègrent également des blocs de mémoire qui facilitent le traitement intégré, bien plus rapide qu'avec des composants externes.

Il existe de nombreux fournisseurs de FPGA, chacun proposant des offres uniques. Parmi eux, Efinix a développé une architecture FPGA spéciale, appelée Quantum, qui convient exclusivement à l'edge computing en général et plus particulièrement au traitement d'images. Autour de cette technologie, la marque a développé sa série de FPGA Trion (et d'ASIC Quantum) pour offrir un avantage puissance-performances-espace multiplié par 4 par rapport aux technologies FPGA traditionnelles (Figure 1). Pour relier les domaines FPGA et ASIC, il existe l'environnement de développement intégré (IDE) Efinity.

Figure 1 : Avec leur avantage puissance-performances-espace, les FPGA Trion conviennent à des applications comme la logique personnalisée, l'accélération du calcul, l'apprentissage automatique, l'apprentissage profond et le traitement d'images. Avec l'IDE Efinity, les utilisateurs peuvent migrer facilement d'un FPGA Trion à un ASIC Quantum pour une production à très haut volume. (Source de l'image : Efinix)

Figure 1 : Avec leur avantage puissance-performances-espace, les FPGA Trion conviennent à des applications comme la logique personnalisée, l'accélération du calcul, l'apprentissage automatique, l'apprentissage profond et le traitement d'images. Avec l'IDE Efinity, les utilisateurs peuvent migrer facilement d'un FPGA Trion à un ASIC Quantum pour une production à très haut volume. (Source de l'image : Efinix)

Présentation de la technologie Quantum

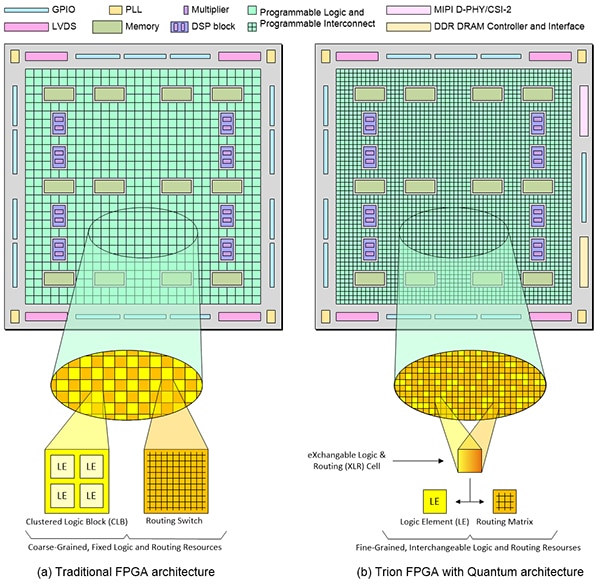

Comme les FPGA traditionnels, les FPGA Trion incluent des blocs de mémoire et des blocs DSP. La différence réside dans la structure programmable (Figure 2). Au cœur de la logique programmable se trouve l'élément logique (LE). Chaque élément logique inclut une table de correspondance (LUT), un multiplexeur et un registre, autant d'éléments pouvant être configurés selon les besoins. Dans le cas des FPGA traditionnels, leur structure programmable peut être décrite comme « approximative ».

Figure 2 : Une architecture FPGA traditionnelle (a) est approximative. Bien que la logique et l'interconnexion soient programmables, elles restent des ressources fixes. En comparaison, les FPGA Trion (b) basés sur l'architecture Quantum sont détaillés. Leur logique et leurs ressources de routage sont interchangeables. (Source de l'image : Max Maxfield)

Figure 2 : Une architecture FPGA traditionnelle (a) est approximative. Bien que la logique et l'interconnexion soient programmables, elles restent des ressources fixes. En comparaison, les FPGA Trion (b) basés sur l'architecture Quantum sont détaillés. Leur logique et leurs ressources de routage sont interchangeables. (Source de l'image : Max Maxfield)

Dans les structures approximatives, plusieurs éléments logiques sont rassemblés dans un bloc logique en cluster (CLB) plus grand. Notez que certains fournisseurs utilisent le terme de bloc logique configurable (CLB) alors que d'autres parlent de bloc de réseau logique (LAB), mais que tous ces termes signifient la même chose.

Il est important de noter que cette illustration est une abstraction. Les blocs CLB et les commutateurs de routage (interconnexion programmable) dans les FPGA traditionnels ne se présentent pas vraiment sous forme de damier comme illustré ici. Toutefois, ils sont fixes et immuables, au sens où la logique et l'interconnexion programmables resteront toujours la logique et l'interconnexion programmables.

Comparés aux architectures traditionnelles, les FPGA Trion sont beaucoup plus détaillés, jusqu'à une résolution d'un seul élément logique. En outre, chaque cellule XLR (Exchangeable Logic and Routing) peut être configurée pour agir comme élément logique ou comme partie de la matrice de routage.

Les cellules de configuration utilisées dans l'architecture Quantum sont basées sur la mémoire SRAM, ce qui signifie que cette technologie est « agnostique au silicium ». Elles peuvent être fabriquées avec tout processus de fabrication CMOS standard, sans avoir besoin d'étapes de traitement spéciales qui sont indispensables aux technologies de configuration alternatives (Flash et antifusible, par exemple) utilisées dans certains FPGA milieu de gamme.

C'est cette interconnexion adaptative hautes performances avec logique et routage configurables par logiciel qui donne à l'approche Quantum une amélioration multipliée par 4 en termes de puissance-performances-espace (PPA) par rapport aux FPGA traditionnels basés SRAM et créés sur le même nœud de technologie de processus.

Par ailleurs, les FPGA créés à l'aide de l'architecture Quantum nécessitent seulement sept couches de métallisation, par opposition aux 12 couches et plus requises par les FPGA traditionnels. Étant donné que chaque couche de métal supplémentaire nécessite plusieurs étapes de masque et de traitement, le fait d'utiliser seulement sept couches réduit les coûts de conception et de fabrication, et augmente le rendement.

Toutes ces caractéristiques et fonctionnalités sont très utiles pour les concepteurs qui cherchent des avantages de coûts, de taille, de performances et de flexibilité pour l'edge computing et le traitement d'images. De ce fait, les FPGA Trion sont parfaitement adaptés aux applications FPGA traditionnelles et aux applications émergentes d'edge computing et de traitement d'images. Ces dernières incluent les applications mobiles, l'Internet des objets (IoT), l'automatisation, la robotique, la fusion de capteurs, la vision par ordinateur, l'IA et le ML.

Structure des FPGA Trion

Les FPGA Trion sont fabriqués sur un processus silicium basse consommation de 40 nanomètres (nm), avec entre 4000 et 200 000 éléments logiques, bien que le processus soit évolutif pour convenir à des dispositifs bien plus volumineux. Tous les FPGA Trion incluent des blocs de mémoire et des blocs DSP, mais leur capacité et leur nombre varient selon la taille du dispositif. Les dispositifs plus compacts comme le T4F81C2 sont plus minimalistes quant à leurs fonctionnalités (3888 LE, 78 848 bits de mémoire et 59 GPIO) et sont destinés à des fonctions de plan de contrôle portables.

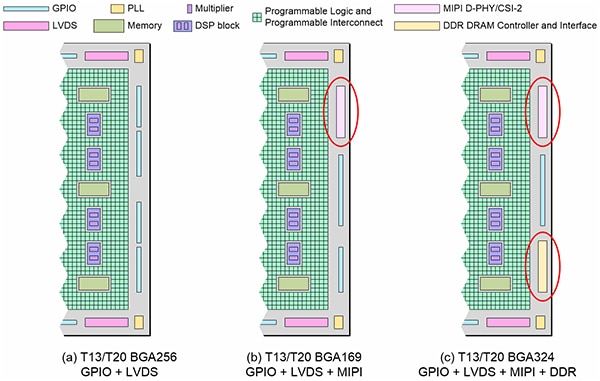

Les dispositifs plus haut de gamme comme le T20F256C3 contiennent proportionnellement plus de ressources (19 728 LE, 1 069 548 bits de mémoire et 195 GPIO). Le T13F256C3 est semblable au T20F256C3, mais comporte 12 828 LE. En outre, les dispositifs comme les T13/T20 sont disponibles dans différentes versions (Figure 3).

Figure 3 : Les dispositifs T13/T20 BGA256 d'Efinix (a) sont des FPGA génériques particulièrement adaptés aux conceptions ayant des exigences E/S intensives. Les dispositifs T13/T20 BGA169 (b) incluent deux blocs MIPI D-PHY/CSI-2 pour les conceptions devant prendre en charge l'interface de caméra MIPI. Les dispositifs T13/T20 BGA324 (c) étendent les interfaces MIPI grâce à une interface DRAM à double débit de données (DDR) x16 bits et à un contrôleur pour les conceptions ayant des besoins intensifs en bande passante mémoire. (Source de l'image : Max Maxfield)

Figure 3 : Les dispositifs T13/T20 BGA256 d'Efinix (a) sont des FPGA génériques particulièrement adaptés aux conceptions ayant des exigences E/S intensives. Les dispositifs T13/T20 BGA169 (b) incluent deux blocs MIPI D-PHY/CSI-2 pour les conceptions devant prendre en charge l'interface de caméra MIPI. Les dispositifs T13/T20 BGA324 (c) étendent les interfaces MIPI grâce à une interface DRAM à double débit de données (DDR) x16 bits et à un contrôleur pour les conceptions ayant des besoins intensifs en bande passante mémoire. (Source de l'image : Max Maxfield)

MIPI CSI-2 est l'interface de caméra la plus largement utilisée dans les systèmes mobiles et d'autres marchés en raison de sa basse consommation, de sa faible latence et de sa connectivité puce-à-puce économique. Elle prend aussi en charge une large gamme de formats hautes performances, notamment la vidéo 1080p, 4K, 8K (et au-delà), ainsi que l'imagerie haute résolution. Ce qui est particulièrement intéressant ici, c'est le fait que MIPI CSI-2 est une interface prédominante, utilisée pour les capteurs de vision dans les applications périphériques. Pour prendre en charge les conceptions pour ces applications, les FPGA T13/T20 BGA169 incluent deux blocs avec cœur matériel MIPI D-PHY/CSI-2 (Figure 3).

La mémoire DDR prend en charge les transferts de données à bande passante élevée, mais nécessite également le respect d'un protocole de temporisation strict. En plus des interfaces MIPI D-PHY/CSI-2 renforcées, les dispositifs Trion T13/T20 BGA324 (Figure 3) incluent également une interface DRAM DDR x16 bits et un contrôleur pour les conceptions ayant des besoins intensifs en bande passante mémoire.

ASIC Quantum

Comme indiqué précédemment, les cellules de configuration utilisées dans les FPGA Trion sont basées sur une mémoire SRAM. Par conséquent, lorsque le système est mis sous tension pour la première fois, les FPGA Trion doivent avoir leurs données de configuration chargées, soit depuis un dispositif de mémoire externe, soit grâce au « bit-banging » via le processeur hôte. Pour ce faire, en production à très haut volume, Efinix propose également des solutions de FPGA embarqués (eFPGA) accélérés par Quantum sous la forme d'ASIC Quantum. Dans ce cas, Efinix peut prendre des conceptions T4, T8, T13 ou T20 et créer des versions ASIC Quantum avec masque qui démarrent en interne sans avoir besoin d'un dispositif de configuration externe.

Conception et développement avec FPGA Trion

Efinix propose une variété de cartes d'évaluation et de kits de développement pour permettre aux utilisateurs de se familiariser avec les FPGA Trion. Ceux-ci incluent le kit de développement Trion T8F81C-DK pour FPGA Trion T8, la carte d'évaluation Trion T20F256C-DK pour FPGA Trion T20, et le kit de développement Trion T20MIPI-DK pour MIPI D-PHY/CSI-2 T20.

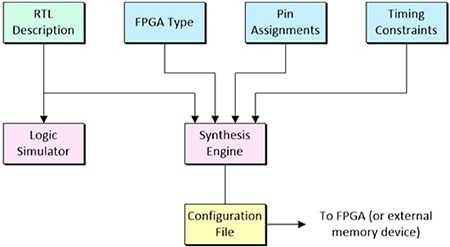

L'une des techniques les plus fréquemment utilisées pour le développement avec des FPGA est la conception basée sur le langage (LDD). Cela implique de capturer l'intention de conception à un niveau d'abstraction connu sous le nom de RTL (Register Transfer Level) à l'aide d'un langage de description de circuit (HDL) comme Verilog ou VHDL. Après vérification par simulation logique, cette représentation est ensuite chargée dans un moteur de synthèse, avec des informations supplémentaires comme le type de FPGA cible, l'affectation des broches et les contraintes temporelles comme les retards entrée-sortie maximum. La sortie du moteur de synthèse est un fichier de configuration qui peut être chargé directement dans le FPGA ou dans un dispositif de mémoire externe (Figure 4).

Figure 4 : Après vérification par simulation logique, la description de conception RTL est chargée dans un moteur de synthèse avec des détails de conception supplémentaires comme le type de FPGA, les affectations de broches et les contraintes temporelles. La sortie du moteur de synthèse est un fichier de configuration qui peut être chargé dans le FPGA. (Source de l'image : Max Maxfield)

Figure 4 : Après vérification par simulation logique, la description de conception RTL est chargée dans un moteur de synthèse avec des détails de conception supplémentaires comme le type de FPGA, les affectations de broches et les contraintes temporelles. La sortie du moteur de synthèse est un fichier de configuration qui peut être chargé dans le FPGA. (Source de l'image : Max Maxfield)

L'IDE Efinity d'Efinix appartient à cette catégorie d'outils. Ce logiciel offre un flux RTL-à-bitstream complet avec une interface utilisateur graphique (GUI) simple et facile à utiliser, et une prise en charge des scripts de lignes de commande. Un tableau de bord intuitif guide le développeur tout au long du flux (synthèse, placement, routage, génération de bitstream), où chaque étape peut être contrôlée automatiquement ou manuellement. Les développeurs peuvent utiliser le moteur de synthèse d'Efinity pour tirer pleinement parti de l'architecture Quantum présente dans les FPGA Trion, afin de générer des dispositifs avec les améliorations puissance-performances-espace multipliées par 4 promises.

En plus de prendre en charge les flux de simulation grâce aux simulateurs ModelSim et NCSim ou au simulateur IVerilog gratuit, l'IDE Efinity présente également un outil de conception d'interface pour restreindre la logique et assigner des broches aux blocs à la périphérie du dispositif, un éditeur de plan de masse pour naviguer dans le placement de la logique et du routage d'une conception, un navigateur de temporisation et une analyse de la temporisation statique pour mesurer les performances d'une conception, ainsi qu'un débogueur matériel intégré avec analyseur logique et cœurs de débogage E/S virtuels.

Conclusion

Alors que les concepteurs effectuent davantage d'opérations de traitement d'images, IA et ML en périphérie, ils doivent, en complément ou en remplacement d'une approche basée cloud, envisager les FPGA comme une partie de leur architecture de traitement, afin de mieux répondre aux problèmes comme les coûts, les performances, la consommation énergétique, la taille, l'évolutivité, la flexibilité et la possibilité de mise à niveau.

Pour certains concepteurs, cela peut impliquer une courbe d'apprentissage, mais comme illustré ici, les avancées FPGA comme la technologie Quantum d'Efinix peuvent rapidement s'avérer rentables grâce à des coûts inférieurs, des formats plus compacts, des performances supérieures et une plus grande flexibilité.

Par conséquent, les FPGA sont maintenant parfaitement adaptés aux applications FPGA traditionnelles ainsi qu'à l'edge computing émergent pour les applications mobiles, IoT, d'automatisation, de robotique, de fusion de capteurs, de vision par ordinateur, d'IA et de ML.

Ressources supplémentaires

- Principes de base : IoT, IIoT, AIoT et en quoi ils représentent l'avenir de l'automatisation industrielle

- Principes de base des FPGA : présentation et rôle des FPGA

- Principes de base des FPGA – 2e partie : premiers pas avec les FPGA de Lattice Semiconductor

- Principes de base des FPGA – 3e partie : premiers pas avec les FPGA de Microchip Technology

Avertissement : les opinions, convictions et points de vue exprimés par les divers auteurs et/ou participants au forum sur ce site Web ne reflètent pas nécessairement ceux de DigiKey ni les politiques officielles de la société.